- Joined

- Dec 18, 2019

- Messages

- 6,447

I would be willing to try a SPI input for the ADC. What SPI rate would be needed?I trawled all the OLD FETs, compared specs, discovered those now supposedly equivalent and overpriced for audiophiles.

Then I found, from Mouser, the SMP147, which of course, is a modern 2SK147.

There was also, from Mouser, the suitable looking NSVJ3557SAT1G.

I did not choose to try for like the Linear Systems LSK389, and LSK170.

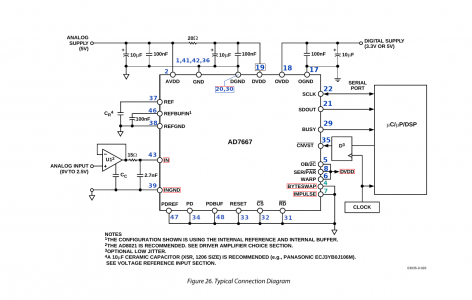

In getting the design together, I am mindful of what other folk might consider essential. For example, if you are using the AD7667, would you be using the recommended AD8021 opamp driver in gain=1 mode as shown in Figure 26.

I trawled all the OLD FETs, compared specs, discovered those now supposedly equivalent and overpriced for audiophiles.

Then I found, from Mouser, the SMP147, which of course, is a modern 2SK147.

There was also, from Mouser, the suitable looking NSVJ3557SAT1G.

I did not choose to try for like the Linear Systems LSK389, and LSK170.

In getting the design together, I am mindful of what other folk might consider essential.

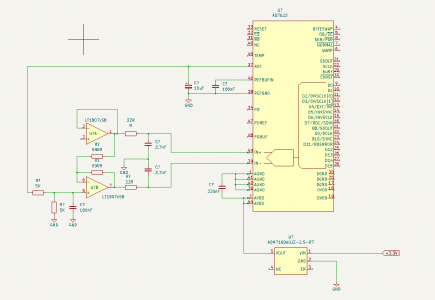

Here we need to check in with @homebrewed . Mark is going to be using the AD7667 ADC,

That ADC uses 2.5V reference. The ADC I use has 2.048V reference, and the power supplies are appropriately different, although that is just a matter of labeling.

If you would also be using the AD7667, would you be using the recommended AD8021 opamp driver in gain=1 mode as shown in Figure 26 ?

The tracking for my differential driver happens to have the same pinout as AD8022 dual driver. It should be easy to arrange the tracking so that it has the driver, and one available opamp for signal conditioning gain.

Mark is interfacing to Teensy, and I think he is grabbing bytes in parallel, so if you are using common software, you would naturally choose to use the AD7667. If you want to be taking off the numbers serially, using SPI, as I intend to, then either will do. I will try to include any stuff you folk request. It is a prototype board anyway. Quite a lot of bits here and there will end up not being populated.

Not so sure about where Fig. 26 is, but I'd probably go for the recommended driver. Generally that's a good idea, especially when just getting things to work.